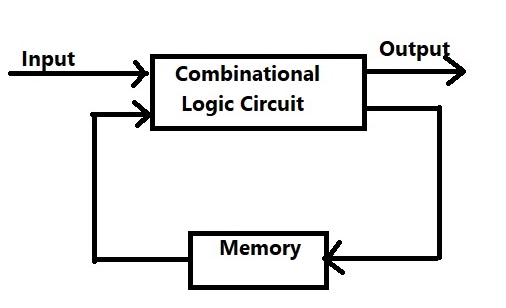

Sequential Logic Circuit এর মেমরি রয়েছে তাই আউটপুট ইনপুটের উপর নির্ভর করে। Sequential Logic Circuit মেমরি উপাদান হিসাবে ফ্লিপ ফ্লপ ব্যবহার করে । এখানে combinational Logic circuit এর সাথে মেমরি/রেজিস্টার সংযুক্ত থাকে। [The sequential Logic Circuit has a memory so output depends on the input. Sequential Logic Circuits use flip-flops as memory elements. ]

Flipflop

Sequential Logic Circuit এর মেমরি উপাদান হিসাবে flipflop ব্যবহার করা হয়। একটি flipflop 1 বিট বাইনারি তথ্য সঞ্চয় করতে ব্যবহৃত হয় । একটি flipflop গঠন করা হয় দুটি NAND gate অথবা NOR gate এর cross couple connection এর মাধ্যমে । ইহার দুটি অবস্থা বর্তমান একটি normal value অন্যটি complement value ।

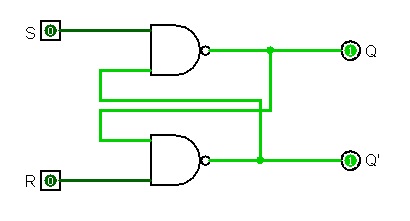

NAND flipflop কার্যনীতিঃ- NAND gate ব্যবহার করে যখন flipflop তৈরি করা হয় তার নিম্ন চারটি case পেয়ে থাকি তা নিম্নরূপ (truth table সহযোগে)

case 1: S=0 এবং R=0 ইনপুট হলে উভয় NAND gate অর্থাৎ S ও R এর মান 1 হয় কিন্তু এটা কখনো সম্ভব নয় কারন আউটপুট দুটি একটি আরেকটির পরিপূরক। তাই এক্ষেত্রে এটি Forbidden state নামে পরিচিত ।

Case 2: S=0 এবং R=1 ইনপুট হলে প্রথম NAND gate অর্থাৎ S এর মান 1 (set=1) এবং দ্বিতীয় NAND gate অর্থাৎ R এর মান 0 (Reset=0)

case 3 S=1 এবং R=0 ইনপুট হলে প্রথম NAND gate অর্থাৎ S এর মান 0 (set=0) এবং দ্বিতীয় NAND gate অর্থাৎ R এর মান 1 (Reset=1)

case 4 S=1 এবং R=1 ইনপুট হলে আউটপুট এর কোনো পরিবর্তন হয় না, বর্তমান অবস্থাতেই পড়ে থাকে ।

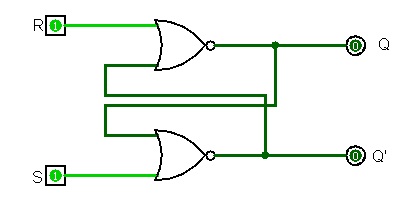

NOR flipflop কার্যনীতিঃ– NOR gate ব্যবহার করে যখন flipflop তৈরি করা হয় তার চারটি case পেয়ে থাকি তা নিম্নরূপ (truth table সহযোগে)।

case 1: S=0 এবং R=0 ইনপুট হলে আউটপুট এর কোনো পরিবর্তন হয় না, বর্তমান অবস্থাতেই পড়ে থাকে ।

Case 2: S=0 এবং R=1 ইনপুট হলে প্রথম NOR gate অর্থাৎ R এর মান 1 (Reset=1) এবং দ্বিতীয় NOR gate অর্থাৎ S এর মান 0 (Set=0)

case 3 S=1 এবং R=0 ইনপুট হলে প্রথম NOR gate অর্থাৎ R এর মান 0 (Reset=0) এবং দ্বিতীয় NOR gate অর্থাৎ S এর মান 1 (Set=1)

case 4 S=1 এবং R=1 ইনপুট হলে উভয় NOR gate অর্থাৎ S ও R এর মান 0 হয় কিন্তু এটা কখনো সম্ভব নয় কারন আউটপুট দুটি একটি আরেকটির পরিপূরক। তাই এক্ষেত্রে এটি Forbidden state নামে পরিচিত ।

Latch

Latch ও flip flop এর ন্যায় একটি electronic circuit যার দুটি অবস্থা বর্তমান ।Latch ও 1 বিট বাইনারি তথ্য সঞ্চয় করতে ব্যবহৃত হয় কিন্তু ল্যাচ(Latch) ফ্লিপ ফ্লপ (Flip flop)এর ন্যায় কোন clock signal প্রদান করা হয় না এবং ইহা clock pulse এর Level Triggered এ কাজ করে। নিম্নলিখিত ভিডিও তে আর ও বিস্তারিত আলোচনা করা হয়েছে। [The latch is also an electronics device that has two states and used to store 1-bit binary data. Latch has no clock connection and it is level triggered. ]

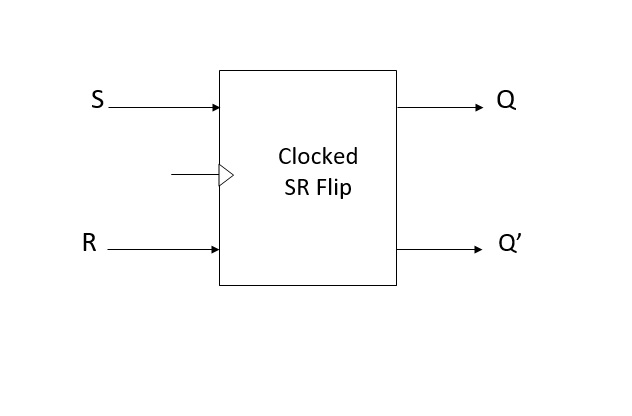

Clocked S-R Flipflop

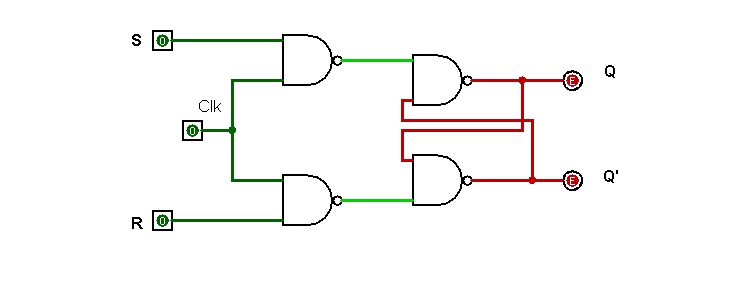

একটি clocked SR flipflop হল এমন এক ধরনের flipflop circuit যার অবস্থা ক্লক সংকেতের(clock signal) পজিটিভ এজে(positive edge) পরিবর্তিত হয়। এর দুটি ইনপুট রয়েছে, যা সাধারণত S (সেট) এবং R (রিসেট) নামে পরিচিত, এবং দুটি আউটপুট, Q এবং Q-bar। clocked SR flipflop circuit এর ডায়াগ্রাম নিম্নলিখিত চিত্রে দেখানো হয়েছে।

কার্যনীতি ব্যাখ্যাঃ–

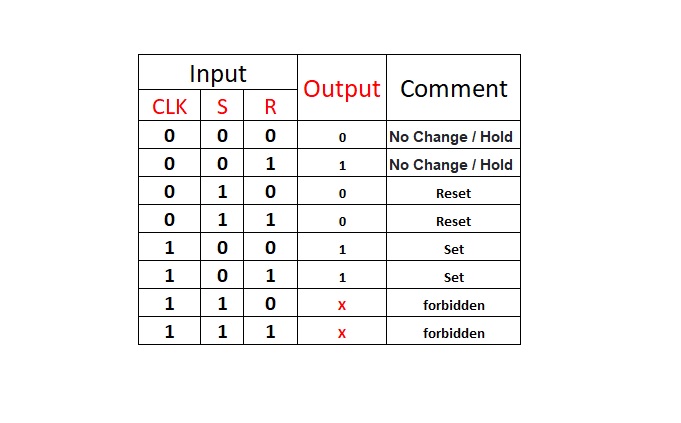

যখন ক্লক সংকেত প্রয়োগ করা হয় না, SR ফ্লিপ-ফ্লপ সার্কিট নিষ্ক্রিয় থাকে, এবং ফ্লিপ-ফ্লপের আউটপুটে কোনও পরিবর্তন হয় না।

যখন ক্লক সংকেত(clock signal) প্রয়োগ করা হয়, ফ্লিপ-ফ্লপ সার্কিট সক্রিয় হয় এবং নিম্নলিখিত ভাবে কাজ করে –

case 1: যখন S = 0 এবং R = 0, NAND গেট 1 এবং 2 এর আউটপুট S’ = 1 এবং R’ = 1। ফলে, NAND গেট 3 এবং 4 এর আউটপুট অপরিবর্তিত থাকে। এটিকে SR ফ্লিপ-ফ্লপের হোল্ড স্টেট(Hold state) বলা হয়।

case 2: যখন S = 0 এবং R = 1, NAND গেট 1 এবং 2 এর আউটপুট S’ = 1 এবং R’ = 0, NAND গেট 3 এর আউটপুট 0 এবং NAND গেট 4 এর আউটপুট 1। এটিকে SR ফ্লিপ-ফ্লপের রিসেট স্টেট (Reset state) বলা হয়।

case 3: যখন S = 1 এবং R = 0, NAND গেট 1 এবং 2 এর আউটপুট S’ = 0 এবং R’ = 1, NAND গেট A এর আউটপুট 1 এবং NAND গেট B এর আউটপুট 0। এটিকে SR ফ্লিপ-ফ্লপের সেট স্টেট (Set state) বলা হয়।

case 4: যখন S = 1 এবং R = 1, NAND গেট 1 এবং 2 এর আউটপুট S’ = 0 এবং R’ = 0, উভয় NAND গেট 3 এবং 4 এর আউটপুট 1 হওয়ার চেষ্টা করে, যা সম্ভব নয়। এটিকে SR ফ্লিপ-ফ্লপের নিষিদ্ধ অবস্থা (Forbidden State) বলা হয়।

SR flip flop এর application

- Digital counters

- Data storage elements

- Storage and shift registers

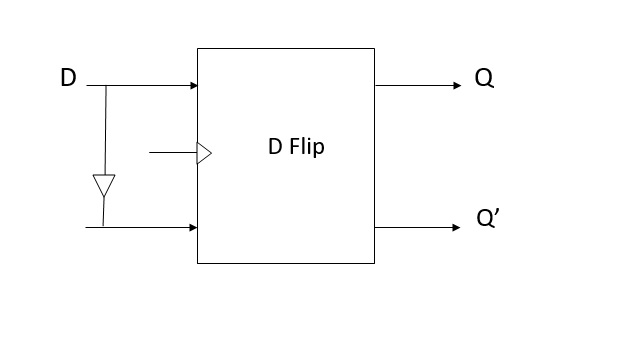

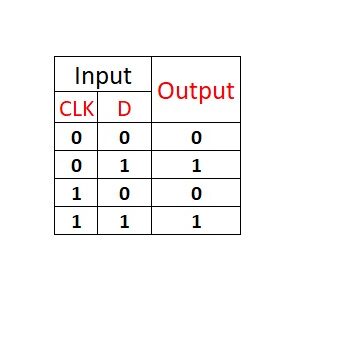

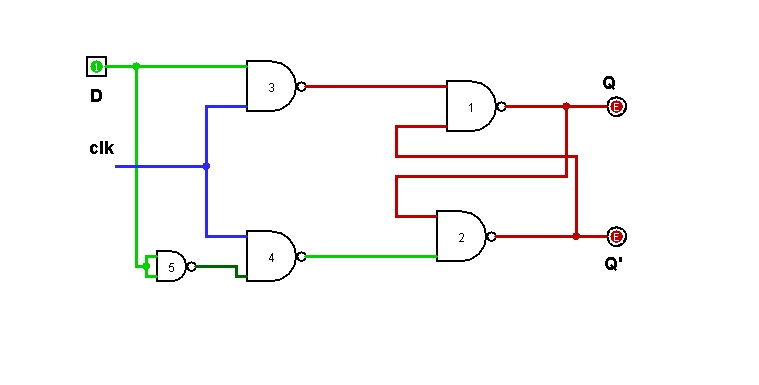

D(Data or Delay)-FlipFlop

D ফ্লিপ-ফ্লপটি হল একটি ক্লকযুক্ত ফ্লিপ-ফ্লপ যেটির একটি একক ‘D’ ডিজিটাল ইনপুট রয়েছে। প্রতিবার D ফ্লিপ-ফ্লপকে ক্লক করা হলে, তার আউটপুট ‘D’ এর অবস্থার অনুসরণ করে। D ফ্লিপ ফ্লপের শুধুমাত্র D এবং CP দুটি ইনপুট রয়েছে। D ইনপুটগুলি ঠিক S ইনপুটে যায় এবং তার পূরক ব্যবহার করা হয় R ইনপুটে। নিম্নলিখিত ভিডিও র মাধ্যমে D flip flop এর সম্পূর্ণ ব্যাখা দেওয়া হয়েছে।D flip flop কে কেন data বা delay ফ্লিপফ্লপ বলা হয়ে থাকে সে বিষয়ে ও আলোকপাত করা হয়েছে।

কার্যনীতি ব্যাখ্যাঃ

clk=0 বিবেচনা করলে, গেট 3 এবং 4 এর আউটপুট 1 স্তরে থাকে এবং D এর মান যাই হোক না কেন, সার্কিট অবস্থার পরিবর্তন করতে পারে না। এখন Clk = 1 এবং D=1 হয়, তাহলে Q এর আউটপুট 1 হয়, যা সার্কিটকে সেট অবস্থায়(set state) আনে। যদি D=0 হয়, তাহলে Q এর আউটপুট 0 হয়, এবং সার্কিট ক্লিয়ার অবস্থায়(clear state) পরিবর্তন হয়।

D flip flop কে delay ফ্লিপফ্লপ বলা হয়ে থাকে কারন D flipflop এ যতক্ষণ না পর্যন্ত positive clock pulse প্রয়োগ করা হয় ততক্ষণ D flipflop data কে ধরে রাখে।

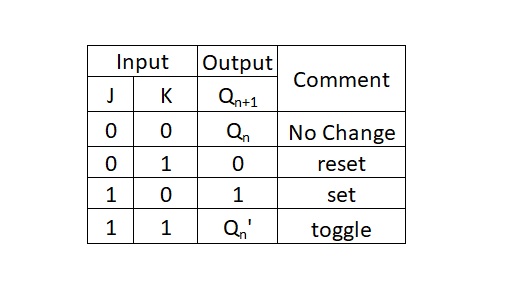

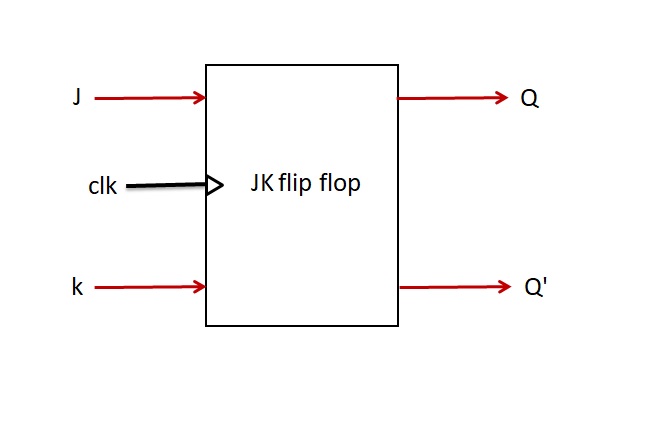

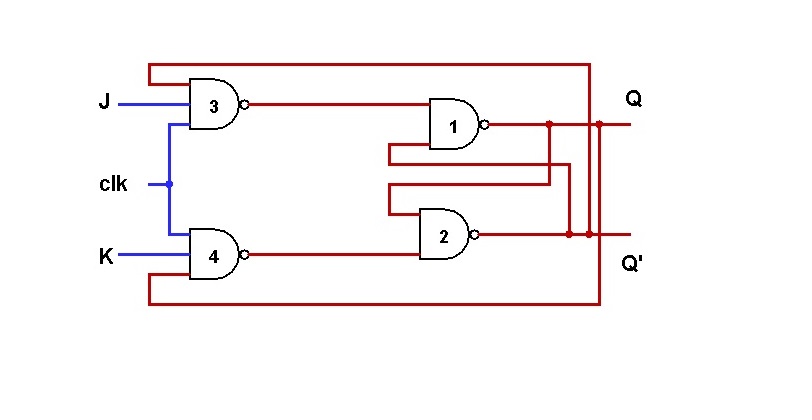

J-K-FlipFlop

JK ফ্লিপ-ফ্লপ এমন একটি ফ্লিপ-ফ্লপ সার্কিট যার দুটি ইনপুট J এবং K এবং দুটি আউটপুট Q এবং Q’ রয়েছে। ফ্লিপ-ফ্লপটি সেট অবস্থা (Q=1, Q’=0) বা রিসেট অবস্থা (Q=0, Q’=1) এ থাকতে পারে।

কার্যনীতি ব্যাখ্যাঃ

ফ্লিপ-ফ্লপের কার্যকারিতা J এবং K ইনপুটের উপর নির্ভর করে:

case 1: J=0, K=0, clock pulse এ অবস্থার কোন পরিবর্তন নেই। Q এবং Q’ একই থাকে।

case 2: J=0, K=1, রিসেট – পরবর্তী clock pulse এ Q=0 হয়ে যায় এবং Q’=1 হয়ে যায়।

case 3: J=1, K=0, সেট – পরবর্তী clock pulse এ Q=1 হয়ে যায় এবং Q’=0 হয়ে যায়।

case 4: J=1, K=1, টগল – পরবর্তী clock pulse এ Q এবং Q’-এর আউটপুট স্টেট টগল/ফ্লিপ( state toggle/flip) হয়।

সুতরাং JK ফ্লিপ-ফ্লপ প্রতিটি clock cycle এ J এবং K ইনপুটের সংমিশ্রণের উপর নির্ভর করে টগল বা তার অবস্থা ধারণ করে। এটি ফ্রিকোয়েন্সি বিভাজন, স্যুইচিং অ্যাপ্লিকেশন, গণনা ইত্যাদির জন্য ব্যবহার করা যেতে পারে।

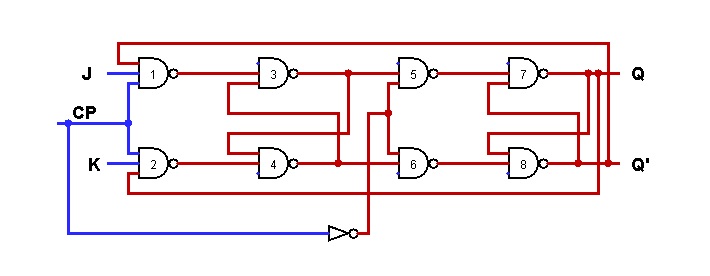

Master -Slave flipflop

মাস্টার-স্লেভ ফ্লিপ ফ্লপটি দুটি JK ফ্লিপ ফ্লপ যোগ করে তৈরি করা হয়। এই দুটি ফ্লিপ ফ্লপের মধ্যে, প্রথম ফ্লিপ ফ্লপটি “মাস্টার” হিসেবে কাজ করে, যা “মাস্টার ফ্লিপ ফ্লপ” হয়, এবং দ্বিতীয়টি “স্লেভ” হিসেবে কাজ করে, যা “স্লেভ ফ্লিপ ফ্লপ” বলে। মাস্টার-স্লেভ ফ্লিপ ফ্লপটি এমনভাবে ডিজাইন করা হয় যে, “মাস্টার” ফ্লিপ ফ্লপের আউটপুটটি “স্লেভ” ফ্লিপ ফ্লপের উভয় ইনপুটে পাঠানো হয়। “স্লেভ” ফ্লিপ ফ্লপের আউটপুটটি মাস্টার ফ্লিপ ফ্লপের ইনপুটে পাঠানো হয়।

“মাস্টার-স্লেভ ফ্লিপ ফ্লপ” এই দুটি ফ্লিপ ফ্লপের বাইরে, একটি ইনভার্টার বা NOT গেটও ব্যবহৃত হয়। সাধারণ ভাষায়, “মাস্টার” এর জন্য CP false হলে, “স্লেভ” এর CP(clock pulse) true হয়, এবং যখন “মাস্টার” এর জন্য CP true হলে , তখন “স্লেভ” এর CP false হয়।

কার্যনীতিঃ

যখন J = 0 এবং K = 0, তবে উভয় JK ফ্লিপ ফ্লপ নিষ্ক্রিয় থাকে এবং সুতরাং আউটপুট Q পরিবর্তন হয় না। এটি মাস্টার-স্লেভ JK ফ্লিপ ফ্লপের হোল্ড স্টেট বলে দেওয়া হয়।

যখন J = 0 এবং K = 1, মাস্টার ফ্লিপ ফ্লপের আউটপুট Q’ Highহয় এবং স্লেভ ফ্লিপ ফ্লপের ইনপুট K তে চলে যায়। ক্লক সিগন্যাল স্লেভ ফ্লিপ ফ্লপ কে রিসেট করতে বাধ্য করে। সুতরাং, স্লেভ ফ্লিপ ফ্লপের আউটপুটটি মাস্টার ফ্লিপ ফ্লপের সাথে একই, অর্থাৎ Q’ high এবং Q low । এটি মাস্টার-স্লেভ JK ফ্লিপ ফ্লপের রিসেট স্টেট বলে দেওয়া হয়।

যখন J = 1 এবং K = 0, মাস্টার ফ্লিপ ফ্লপের আউটপুট Q High হয় এবং স্লেভ ফ্লিপ ফ্লপের ইনপুট J তে চলে যায়, ক্লক সিগন্যালের নেগেটিভ ট্রানজিশন স্লেভ ফ্লিপ ফ্লপ কে সেট করে। সুতরাং, এটি মাস্টার-স্লেভ JK ফ্লিপ ফ্লপের সেট স্টেট বলে দেওয়া হয়।

যখন J = 1 এবং K = 1, মাস্টার ফ্লিপ ফ্লপ ক্লক পাল্সের পজিটিভ ট্রানজিশনে টগল হয় এবং স্লেভ ফ্লিপ ফ্লপ ঘড়ি পাল্সের নেগেটিভ ট্রানজিশনে টগল হয়। সুতরাং, JK ফ্লিপ ফ্লপের রেস আরাউন্ড(Race around)condition এর সমস্যা সমাধান হয়।